# CMOS 18-BIT TTL/GTLP UNIVERSAL BUS TRANSCEIVER

# IDT74GTLP16612 PRELIMINARY

## **FEATURES:**

- · Bidirectional interface between GTLP and TTL logic levels

- · Edge Rate Control Circuit reduces output noise

- · VREF pin provides reference voltage for receiver threshold

- CMOS technology for low power dissipation

- Special PVT Compensation circuitry to provide consistent performance over variations of process, supply voltage, and temperature

- 5V tolerant inputs and outputs on A-Port

- Bus-Hold to eliminate the need for external pull-up resistors for unused inputs to A-Port

- · Power up/down high-impedance

- · TTL-compatible Driver and Control inputs

- · High Output source/sink ±32mA on A-Port pins

- · Flow-through architecture optimizes system layout

- D-type latch and flip-flop architecture for data flow in clocked, transparent, or latched mode

- · Open drain on GTLP to support wired OR connection

- · Available in SSOP and TSSOP packages

## **DESCRIPTION:**

The GTLP16612 is an 18-bit universal bus transceiver. It provides signal level translation, from TTL to GTLP, for applications requiring a high-speed interface between cards operating at TTL logic levels and backplanes operating at GTLP logic levels. GTLP provides reduced output swing (<1V), reduced input threshold levels, and output edge-rate control to minimize signal setting times. The GTLP16612 is a derivative of the Gunning Transceiver Logic (GTL) JEDEC standard JESD8-3 and incorporates internal edge-rate control, which is process, voltage, and temperature (PVT) compensated.

GTLP output low voltage is less than 0.5V. The output high is 1.5V, and the receiver threshold is 1V.

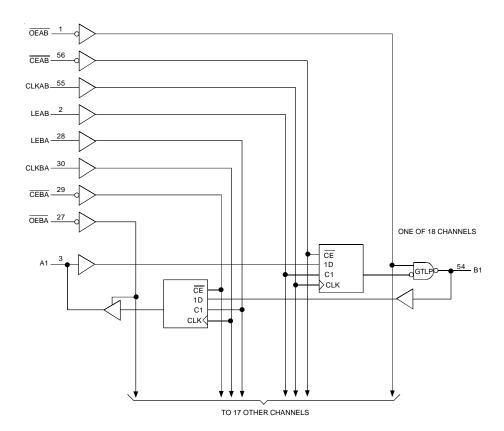

## FUNCTIONAL BLOCK DIAGRAM

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

INDUSTRIAL TEMPERATURE RANGE

OCTOBER 1999

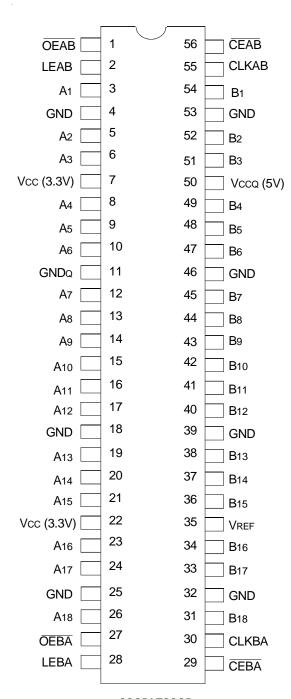

## **PIN CONFIGURATION**

SSOP/ TSSOP TOP VIEW

# ABSOLUTE MAXIMUM RATINGS(1,2)

| Symbol | Rating                                   | Max.              | Unit |

|--------|------------------------------------------|-------------------|------|

| Vcc    | SupplyVoltage                            | -0.5 to +7        | V    |

| Vccq   |                                          |                   |      |

| Vı     | DC Input Voltage                         | -0.5 to +7        | V    |

| Vo     | DC Output Voltage, 3-State               | -0.5 to +7        | V    |

| Vo     | DC Output Voltage, Active                | -0.5 to Vcc + 0.5 | V    |

| lol    | DC Output Sink Current into A-port       | 64                | mA   |

| Іон    | loн DC Output Source Current from A-port |                   | mA   |

| lol    | DC Output Sink Current into B-port       | 80                | mA   |

|        | (in the LOW state)                       |                   |      |

| lık    | Iıк DC Input Diode Current Vı < 0V       |                   | mA   |

| Іок    | DC Output Diode Current Vo < 0V          | -50               | mA   |

| Іок    | DC Output Diode Current Vo > Vcc         | +50               | mA   |

| Tstg   | Storage Temperature                      | -65 to +150       | °C   |

#### NOTES:

- Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. This is a stress rating only and functional operation

of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

- 2. Unused inputs without Bus-Hold must be held HIGH or LOW.

# CAPACITANCE (TA = +25°C, f = 1.0MHz)

| Symbol | Parameter <sup>(1)</sup> | Conditions     | Typ. <sup>(2)</sup> | Max. | Unit |

|--------|--------------------------|----------------|---------------------|------|------|

| Cin    | Control Pins             | VI = Vccq or 0 | 8                   | _    | pF   |

| Cı/o   | A-Port                   | VI = Vccq or 0 | 9                   | _    | pF   |

| Cı/o   | B-Port                   | VI = Vccq or 0 | 6                   | _    | pF   |

## NOTES:

- 1. As applicable to the device type.

- 2. All typical values are at Vcc = 3.3V and Vcco = 5V.

# **PIN DESCRIPTION**

| Pin Names | Description <sup>(1)</sup>                           |

|-----------|------------------------------------------------------|

| ŌĒĀB      | A-to-B Output Enable (Active LOW)                    |

| ŌĒBĀ      | B-to-A Output Enable (Active LOW)                    |

| CEAB      | A-to-B Clock Enable (Active LOW)                     |

| CEBA      | B-to-A Clock Enable (Active LOW)                     |

| LEAB      | A-to-B Latch Enable (Transparent HIGH)               |

| LEBA      | B-to-A Latch Enable (Transparent HIGH)               |

| CLKAB     | A-to-B Clock Pulse                                   |

| CLKBA     | B-to-A Clock Pulse                                   |

| Vref      | GTLP Input Reference Voltage                         |

| A1 - A18  | A-to-BTTL Data Inputs or B-to-A 3-State Outputs      |

| B1 - B18  | B-to-A GTLP Data Inputs or A-to-B Open Drain Outputs |

#### NOTE:

1. A-Port pins have Bus-Hold. All other pins are standard input, output, or I/O.

# RECOMMENDED OPERATING CONDITIONS<sup>(1)</sup>

| Symbol | Rating                                   | Recommended  | Unit |

|--------|------------------------------------------|--------------|------|

| Vcc    | Supply Voltage                           | 3.15 to 3.45 | V    |

| Vcca   |                                          | 4.75 to 5.25 |      |

| VTT    | Bus Termination Voltage                  | 1.35 to 1.65 | V    |

| Vı     | Input Voltage on A-Port and Control Pins | 0 to 5.5     | V    |

| Іон    | HIGH Level Output Current (A-Port)       | -32          | mA   |

| loL    | LOW Level Output Current (A-Port)        | +32          | mA   |

| loL    | LOW Level Output Current (B-Port)        | +34          | mA   |

| TA     | Operating Temperature                    | -40 to +85   | °C   |

# FUNCTIONAL DESCRIPTION:

The GTLP16612 combines a universal transceiver function with a TTL to GTLP translation. The A-Port and control pins operate at LVTTL or 5V TTL levels while the B-Port operates at GTLP levels. The transceiver logic includes D-type latches and D-type flip-flops to allow data flow in transparent, latched, and clock mode.

#### NOTE:

1. Unused inputs without Bus-Hold must be held HIGH or LOW.

## FUNCTION TABLE(1,2)

| Inputs |             |      |          | Outputs | Mode                          |                 |

|--------|-------------|------|----------|---------|-------------------------------|-----------------|

| CEAB   | <u>ŌĒĀB</u> | LEAB | CLKAB    | Ах      | Вх                            |                 |

| X      | Н           | Χ    | X        | Х       | Z                             | Latched         |

| L      | L           | L    | Н        | Х       | B <sub>0</sub> <sup>(3)</sup> | storage         |

| L      | L           | L    | L        | Х       | B <sub>0</sub> <sup>(4)</sup> | of A data       |

| Х      | L           | Н    | X        | L       | L                             | Transparent     |

| Х      | L           | Н    | X        | Н       | Н                             |                 |

| L      | L           | L    | <b>↑</b> | L       | L                             | Clocked storage |

| L      | L           | L    | <b>↑</b> | Н       | Н                             | of A data       |

| Н      | L           | L    | Х        | Χ       | B <sub>0</sub> <sup>(4)</sup> | Clock Inhibit   |

#### NOTES:

- 1. H = HIGH Voltage Level

- L = LOW Voltage Level

- X = Don't Care

- ↑ = LOW-to-HIGH Transition

- 2. A-to-B data flow is shown. B-to-A data flow is similar, but uses OEBA, LEBA, CLKBA, and CEBA.

- 3. Output level before the indicated steady-state input conditions were established, provided that CLKAB was HIGH before LEAB went LOW.

- 4. Output level before the indicated steady-state input conditions were established.

## DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

$Following\ Conditions\ Apply\ Unless\ Otherwise\ Specified:$

Industrial: TA = -40°C to +85°C, VREF = 1V, VCC = 3.3V  $\pm$  5%, VCCQ = 5V  $\pm$  5%

| Symbol              | Parameter               | Test Conditions                       |                   | Min.      | Typ. <sup>(1)</sup> | Max.       | Unit |

|---------------------|-------------------------|---------------------------------------|-------------------|-----------|---------------------|------------|------|

| VIH                 | B-Port                  |                                       |                   | VREF+ 0.1 | _                   | Vtt        | V    |

|                     | All Other ports         |                                       |                   | 2         | _                   | _          |      |

| VIL                 | B-Port                  | _                                     |                   | 0         | _                   | VREF-0.1   | V    |

|                     | All Other ports         | _                                     |                   | _         | _                   | 0.8        |      |

| Vref                | _                       | _                                     |                   | _         | 1                   | _          | V    |

| Vik                 | _                       | Vcc = 3.                              | 5V Iı = –18mA     | _         | _                   | -1.2       | V    |

|                     |                         | Vccq = 4                              | .75V              |           |                     |            |      |

| Voн                 | A-Port                  | Vcc, Vccq = Min to Max <sup>(2)</sup> | Iон = -100µА      | Vcc-0.2   | _                   | _          |      |

|                     |                         | Vcc = 3.15V                           | Іон = -8mA        | 2.4       | _                   | _          | V    |

|                     |                         | Vccq = 4.75V                          | Іон = –32mA       | 2         | _                   | _          |      |

| Voн                 | A-Port                  | Vcc, Vccq = Min to Max <sup>(2)</sup> | IoL = 100µA       | _         | _                   | 0.2        |      |

|                     |                         | Vcc = 3.15V                           | IoL = 32mA        | _         | _                   | 0.5        |      |

|                     |                         | Vccq = 4.75V                          |                   |           |                     |            | V    |

|                     | B-Port                  | Vcc = 3.15V                           | IoL = 34mA        | _         | _                   | 0.65       |      |

|                     |                         | Vccq = 4.75V                          |                   |           |                     |            |      |

| lı                  | Control Pins            | Vcc, Vccq = 0 or Max                  | Vı = 5.5V or 0V   | _         | _                   | ±10        |      |

|                     | A-Port                  | Vcc = 3.45V                           | Vı = 5.5V         | _         | _                   | 20         |      |

|                     |                         | Vccq = 5.25V                          | VI = VCC          | _         | _                   | 1          | μA   |

|                     |                         |                                       | Vı = 0            | _         | _                   | -30        |      |

|                     | B-Port                  | Vcc = 3.45V                           | VI = VCCQ         | _         | _                   | 5          |      |

|                     |                         | Vccq = 5.25V                          | Vı = 0            | _         | _                   | <b>-</b> 5 |      |

| loff                | A-Port                  | Vcc = Vccq = 0 Vi or Vo = 0 to 4.5V   |                   | _         | _                   | 100        | μΑ   |

| lı (HOLD)           | A-Port                  | Vcc = 3.15V                           | Vı = 0.8V         | 75        | _                   | _          | μΑ   |

|                     |                         | Vccq = 4.75V                          | Vı = 2V           | -20       | _                   | _          |      |

| lozн                | A-Port                  | Vcc = 3.45V                           | Vo = 3.45 V       |           | _                   | 1          | μΑ   |

|                     | B-Port                  | Vccq = 5.25V                          | Vo = 1.5V         | _         | _                   | 5          |      |

| lozl                | A-Port                  | Vcc = 3.45V                           | Vo = 0            | -         |                     | -20        | μΑ   |

|                     | B-Port                  | Vccq = 5.25V                          | Vo = 0.65V        | _         | _                   | -10        |      |

| Icca (Vcca)         | A or B Ports            | Vcc = 3.45V                           | Outputs HIGH      | _         | 30                  | 40         |      |

|                     |                         | Vccq = 5.25V                          | Outputs LOW       | _         | 30                  | 40         | mA   |

|                     |                         | lo = 0                                |                   |           |                     |            |      |

|                     |                         | VI = VCCQ or GND                      | Outputs Disabled  | _         | 30                  | 40         |      |

| Icc (Vcc)           | A or B Ports            | Vcc = 3.45V                           | Outputs HIGH      | 1         | 0                   | 1          |      |

|                     |                         | Vccq = 5.25V                          | Outputs LOW       | _         | 0                   | 1          | mA   |

|                     |                         | lo = 0                                |                   |           |                     |            |      |

|                     |                         | VI = VCCQ or GND                      | Outputs Disabled  | _         | 0                   | 1          |      |

| ∆lcc <sup>(3)</sup> | A-Port and Control Pins | Vcc = 3.45V                           | One Input at 2.7V | _         | 0                   | 1          | mA   |

|                     |                         | Vccq = 5.25V                          |                   |           |                     |            |      |

|                     |                         | A or Control Inputs at                |                   |           |                     |            |      |

|                     |                         | Vcc or GND                            |                   |           |                     |            |      |

### NOTES:

- 1. All typical values are at Vcc = 3.3V, Vccq = 5V, and TA = 25°C.

- 2. For conditions shown as Max. or Min., use appropriate value specified under Recommended Operating Conditions.

- 3.  $\Delta lcc$  is the increase in supply current for each input that is at the specified TTL voltage level rather than Vcc or GND.

# SWITCHING CHARACTERISTICS OVER OPERATING RANGE $^{(1,2)}$

|        |                                            |      | IDT74GTLP16612      |      |      |  |

|--------|--------------------------------------------|------|---------------------|------|------|--|

| Symbol | Parameter                                  | Min. | Тур. <sup>(3)</sup> | Max. | Unit |  |

| fclock | Max Clock Frequency                        | 175  | _                   | _    | MHz  |  |

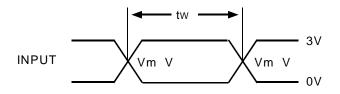

| tw     | Pulse Duration, LEAB or LEBA HIGH          | 3    | _                   | _    | ns   |  |

| tw     | Pulse Duration, CLKAB or CLKBA HIGH or LOW | 3.2  | _                   | _    |      |  |

| ts     | Setup Time, Ax before CLKAB ↑              | 0.5  | _                   | _    |      |  |

| ts     | Setup Time, Bx before CLKBA ↑              | 3.1  | _                   | _    |      |  |

| ts     | Setup Time, Ax before LEAB ↓               | 1.3  | _                   | _    | ns   |  |

| ts     | Setup Time, Bx before LEBA ↓               | 3.7  | _                   | _    |      |  |

| ts     | Setup Time, CEAB before CLKAB ↑            | 0.4  | _                   | _    |      |  |

| ts     | Setup Time, CEBA beforeCLKBA ↑             | 1    | _                   | _    | 1    |  |

| tн     | Hold Time, Ax after CLKAB ↑                | 1.5  | _                   | _    |      |  |

| tн     | Hold Time, Bx after CLKBA ↑                | 0    | _                   | _    |      |  |

| t⊢     | Hold Time, Ax after LEAB ↓                 | 0.5  | _                   | _    | ns   |  |

| tн     | Hold Time, Bx after LEBA ↓                 | 0    | _                   | _    |      |  |

| tн     | Hold Time, CEAB after CLKAB ↑              | 1.5  | _                   | _    |      |  |

| t⊢     | Hold Time, CEBA afterCLKBA ↑               | 1.7  | _                   | _    | 1    |  |

| tplh   | Ax to Bx                                   | 1    | 4.3                 | 6.5  | ns   |  |

| tphl   |                                            | 1    | 5                   | 8.2  |      |  |

| tplh   | LEAB to Bx                                 | 1.8  | 4.5                 | 6.7  | ns   |  |

| tphl   |                                            | 1.5  | 5.3                 | 8.6  |      |  |

| tplh   | CLKAB to Bx                                | 1.8  | 4.6                 | 6.7  | ns   |  |

| tphl   |                                            | 1.5  | 5.4                 | 8.7  |      |  |

| tplh   | OEAB to Bx                                 | 1.6  | 4.4                 | 6.2  | ns   |  |

| tphl   |                                            | 1.3  | 6.1                 | 9.8  |      |  |

| trise  | Transition Time, B outputs (20% to 80%)    | _    | 2.6                 | _    | ns   |  |

| tfall  |                                            |      |                     |      |      |  |

| tplh   | Bx to Ax                                   | 2    | 5.6                 | 8.2  | ns   |  |

| tphl   |                                            | 1.4  | 5                   | 7.2  | 1    |  |

| tplh   | LEBA to Ax                                 | 2.1  | 4.2                 | 6.3  | ns   |  |

| tphl   |                                            | 1.9  | 3.3                 | 5    |      |  |

| tplh   | CLKBA to Ax                                | 2.3  | 4.4                 | 6.8  | ns   |  |

| tphl   |                                            | 2.2  | 3.5                 | 5.2  |      |  |

| tpzh   | OEBA to Ax                                 | 1.5  | 5                   | 6.2  |      |  |

| tPZL   |                                            |      |                     |      |      |  |

| tphz   |                                            | 1.9  | 3.9                 | 7.9  | ns   |  |

| tplz   |                                            |      |                     |      |      |  |

## NOTES:

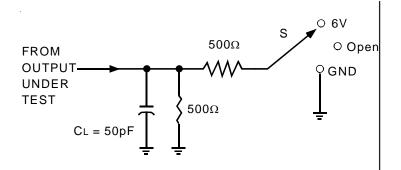

- 1. See Test Circuits and Waveforms. TA = -40°C to +85°C.

- 2. Unless otherwise noted,  $V_{REF}$  = 1V,  $C_L$  = 30pF for B-Port, and  $C_L$  = 50pF for A-Port.

- 3. Typical values are at Vcc = 3.3V, Vccq = 5V, and TA = 25°C.

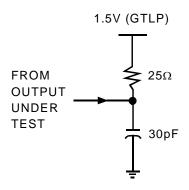

# TEST CIRCUITS AND WAVEFORMS

#### NOTE:

1. CL includes probes and jig capacitance.

Test Circuit for A Outputs(1)

# **SWITCH POSITION**

| Test            | Switch |

|-----------------|--------|

| Open Drain      |        |

| Disable Low     | 6V     |

| Enable Low      |        |

| Disable High    | GND    |

| Enable High     |        |

| All Other Tests | Open   |

Voltage Waveforms Pulse Duration (Vm = 1.5V for A-Port and 1V for B-Port)

#### NOTE:

1. CL includes probes and jig capacitance. For B-Port outputs, CL = 30pF is used for worst case edge rate.

Test Circuit for B Outputs(1)

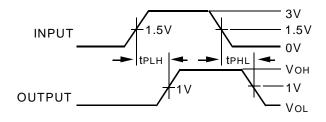

Voltage Waveforms Propagation Delay Times (A-Port to B-Port)

#### NOTE:

All input pulses have the following characteristics: frequency = 10 MHz,  $t_R = t_F = 2$  ns,  $Z_0 = 50\Omega$ . The outputs are measured one at a time with one transition per measurement.

## TEST CIRCUITS AND WAVEFORMS

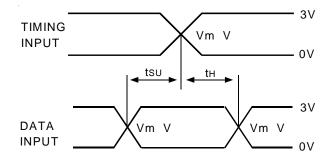

Voltage Waveforms Setup and Hold Times (Vm = 1.5V for A-Port and 1V for B-Port)

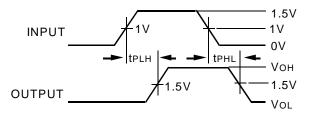

Voltage Waveforms Propagation Delay Times (B-Port to A-Port)

#### NOTE:

All input pulses have the following characteristics: frequency = 10 MHz,  $t_R = t_F = 2$  ns,  $Z_O = 50\Omega$ . The outputs are measured one at a time with one transition per measurement.

Voltage Waveforms Enable and Disable Times (A-Port)

#### NOTE:

Waveform 1 is for an output with internal conditions such that the output is LOW except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is HIGH except when disabled by the output control.

All input pulses have the following characteristics: frequency = 10 MHz, t<sub>R</sub> = t<sub>F</sub> = 2 ns, Z<sub>O</sub> = 50Ω. The outputs are measured one at a time with one transition per measurement.

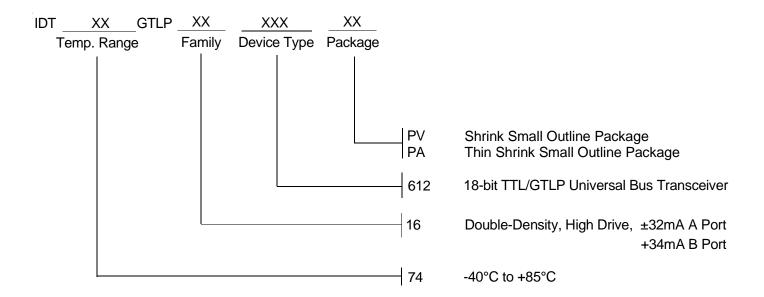

# ORDERING INFORMATION

2975 Stender Way Santa Clara, CA 95054 for SALES:

800-345-7015 or 408-727-6116 fax: 408-492-8674 www.idt.com

for Tech Support: logichelp@idt.com (408) 654-6459